# CX84100-41/-23 SCXV.22bis Modem V.22bis Modem with CX20493 SmartDAA® Line Side Device

**Data Sheet**

#### **Revision Record**

| Revision | Date      | Comments         |

|----------|-----------|------------------|

| С        | 3/3/2004  | Rev. C release.  |

| В        | 12/9/2003 | Rev. B release.  |

| Α        | 12/3/2003 | Initial release. |

© 2003, 2004 Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant® and the Conexant C symbol, and SmartDAA®. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com, which is incorporated by reference.

**Reader Response:** Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

# **Contents**

| 1. | Intro | duction  |                                                   | 1-1 |

|----|-------|----------|---------------------------------------------------|-----|

|    | 1.1   | Overvie  | ew                                                | 1-1 |

|    | 1.2   | Feature  | s                                                 | 1-3 |

|    |       | 1.2.1    | SmartDAA Features                                 | 1-4 |

|    |       | 1.2.2    | Applications                                      | 1-4 |

|    | 1.3   | Technic  | cal Overview                                      | 1-5 |

|    |       | 1.3.1    | General Description                               | 1-5 |

|    |       | 1.3.2    | MCU                                               | 1-5 |

|    |       | 1.3.3    | Operating Modes                                   | 1-5 |

|    |       |          | 1.3.3.1 Data Modes                                | 1-5 |

|    |       |          | 1.3.3.2 Worldwide Operation                       | 1-5 |

|    |       | 1.3.4    | Reference Design                                  | 1-6 |

|    | 1.4   | Hardwa   | are Description                                   | 1-7 |

|    |       | 1.4.1    | CX84100 V.22bis Modem                             | 1-7 |

|    |       | 1.4.2    | Digital Isolation Barrier                         | 1-7 |

|    |       | 1.4.3    | CX20493 SmartDAA Line Side Device                 | 1-7 |

|    | 1.5   | Comma    | ands                                              | 1-8 |

| 2. | Tech  | nical Sp | pecifications                                     | 2-1 |

|    | 2.1   | Serial D | 2-1                                               |     |

|    |       | 2.1.1    | Automatic Speed/Format Sensing                    | 2-1 |

|    | 2.2   | Establis | shing Data Modem Connections                      | 2-2 |

|    |       | 2.2.1    | Dialing                                           | 2-2 |

|    |       | 2.2.2    | Modem Handshaking Protocol                        | 2-2 |

|    |       | 2.2.3    | Call Progress Tone Detection                      | 2-2 |

|    |       | 2.2.4    | Answer Tone Detection                             | 2-2 |

|    |       | 2.2.5    | Ring Detection                                    | 2-2 |

|    |       | 2.2.6    | Billing Protection                                | 2-2 |

|    |       | 2.2.7    | Connection Speeds                                 | 2-2 |

|    |       | 2.2.8    | Automode                                          | 2-3 |

|    | 2.3   | Data Mo  | ode                                               | 2-3 |

|    |       | 2.3.1    | Speed Buffering (Normal Mode)                     | 2-3 |

|    |       | 2.3.2    | Flow Control                                      | 2-3 |

|    |       | 2.3.3    | Direct Mode                                       | 2-3 |

|    |       | 2.3.4    | Escape Sequence Detection                         | 2-4 |

|    |       | 2.3.5    | Telephone Line Monitoring                         | 2-4 |

|    |       | 2.3.6    | Retrain                                           | 2-4 |

|    |       | 2.3.7    | Programmable Inactivity Timer                     | 2-4 |

|    |       | 2.3.8    | DTE Signal Monitoring (Serial DTE Interface Only) | 2-4 |

|    | 2.4  | Error Correction and Data Compression                                        | 2-4 |  |

|----|------|------------------------------------------------------------------------------|-----|--|

|    |      | 2.4.1 V.42 Error Correction                                                  | 2-4 |  |

|    |      | 2.4.2 MNP 2-4 Error Correction                                               | 2-4 |  |

|    |      | 2.4.3 V.42 bis Data Compression                                              | 2-5 |  |

|    | 2.5  | Telephony Extensions                                                         | 2-5 |  |

|    |      | 2.5.1 Line In Use Detection                                                  | 2-5 |  |

|    |      | 2.5.2 Extension Pickup Detection                                             | 2-5 |  |

|    |      | 2.5.3 Remote Hangup Detection                                                | 2-5 |  |

|    |      | 2.5.4 Digital Line Protection                                                | 2-5 |  |

|    | 2.6  | Caller ID                                                                    | 2-6 |  |

|    |      | 2.6.1 Type II CID                                                            | 2-6 |  |

|    | 2.7  | Worldwide Country Support                                                    | 2-6 |  |

|    | 2.8  | Diagnostics                                                                  | 2-7 |  |

|    |      | 2.8.1 Commanded Tests                                                        | 2-7 |  |

|    | 2.9  | Low Power Mode                                                               | 2-7 |  |

| 3. | Hard | dware Interface                                                              | 3-1 |  |

| ٠. | 3.1  | CX84100 V.22bis Modem Hardware Pins and Signals                              |     |  |

|    | 0.1  | 3.1.1 CX84100 V.22bis Modern Signal Summary                                  |     |  |

|    |      | 3.1.1.1 CX20493 LSD Interface (Through DIB)                                  |     |  |

|    |      | 3.1.1.2 Call Progress Speaker Interface                                      |     |  |

|    |      | 3.1.1.3 Serial DTE Interface and Indicator Outputs                           |     |  |

|    |      | 3.1.1.4 Control and Signals                                                  |     |  |

|    |      | 3.1.1.5 Crystal/Clock and Power Signals                                      |     |  |

|    |      | 3.1.2 CX84100 V.22bis Modem Pin Assignments and Signal Definitions           |     |  |

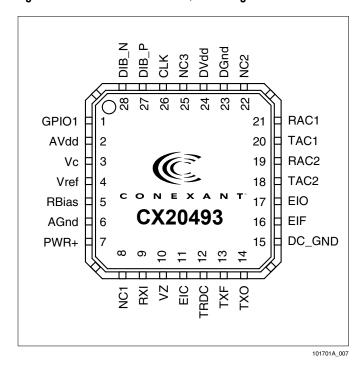

|    | 3.2  | CX20493 LSD 28-Pin QFN Hardware Pins and Signals                             |     |  |

|    | 0.2  | 3.2.1 CX20493 LSD 28-Pin QFN Signal Summary                                  |     |  |

|    |      | 3.2.1.1 CX84100 V.22bis Modem Interface (Through DIB)                        |     |  |

|    |      | 3.2.1.2 Telephone Line Interface                                             |     |  |

|    |      | 3.2.1.3 Voltage References                                                   |     |  |

|    |      | 3.2.1.4 General Purpose Input/Output                                         |     |  |

|    |      | 3.2.1.5 No Connects                                                          |     |  |

|    |      | 3.2.2 CX20493 LSD 28-Pin QFN Pin Assignments and Signal Definitions          |     |  |

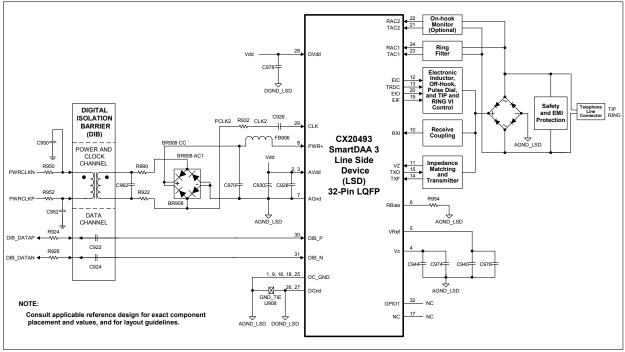

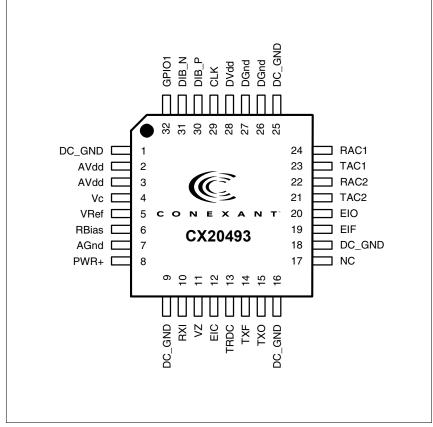

|    | 3.3  | CX20493 LSD 32-Pin LQFP Hardware Pins and Signals                            |     |  |

|    | 0.0  | 3.3.1 CX20493 LSD 32-Pin LQFP Signal Summary                                 |     |  |

|    |      | 3.3.1.1 CX84100 Interface (Through DIB)                                      |     |  |

|    |      | 3.3.1.2 Telephone Line Interface                                             |     |  |

|    |      | 3.3.1.3 Voltage References                                                   |     |  |

|    |      | 3.3.1.4 General Purpose Input/Output                                         |     |  |

|    |      | 3.3.1.5 No Connects                                                          |     |  |

|    |      | 3.3.2 CX20493 LSD 32-Pin LQFP Pin Assignments and Signal Definitions         |     |  |

|    | 3.4  | CX20493 LSD GPIO DC Electrical Characteristics                               |     |  |

|    | 3.5  | Electrical and Environmental Specifications                                  |     |  |

|    | 0.0  | 3.5.1 Operating Conditions, Absolute Maximum Ratings, and Power Requirements |     |  |

|    | 3.6  | Interface Timing and Waveforms                                               |     |  |

|    | 5.5  | 3.6.1.1 Serial DTE Interface                                                 |     |  |

|    | 3.7  | Crystal Specifications                                                       |     |  |

| 4  |      | cage Dimensions                                                              | Δ-1 |  |

|    |      |                                                                              |     |  |

# **Figures**

| Figure 1-1. SCXV.22bis Modem Simplified Interface Diagram      | 1-2  |

|----------------------------------------------------------------|------|

| Figure 1-2. SCXV.22bis Modem Major Interfaces                  | 1-2  |

| Figure 3-1. CX84100 V.22bis Modem Hardware Interface Signals   | 3-2  |

| Figure 3-2. CX84100 V.22bis Modem 28-Pin TSSOP Pin Signals     | 3-3  |

| Figure 3-3. CX20493 LSD 28-Pin QFN Hardware Interface Signals  | 3-9  |

| Figure 3-4. CX20493 LSD 28-Pin QFN Pin Signals                 | 3-10 |

| Figure 3-5. CX20493 LSD 32-Pin LQFP Hardware Interface Signals | 3-14 |

| Figure 3-6. CX20493 LSD 32-Pin LQFP Pin Signals                | 3-15 |

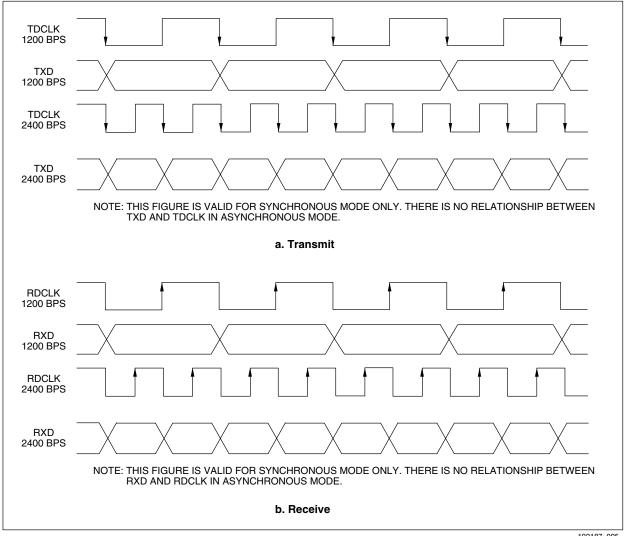

| Figure 3-7. Waveforms - Serial DTE Interface                   | 3-2  |

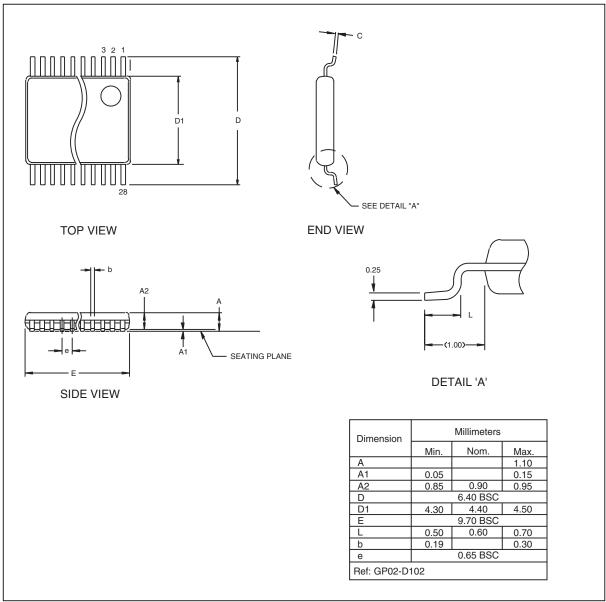

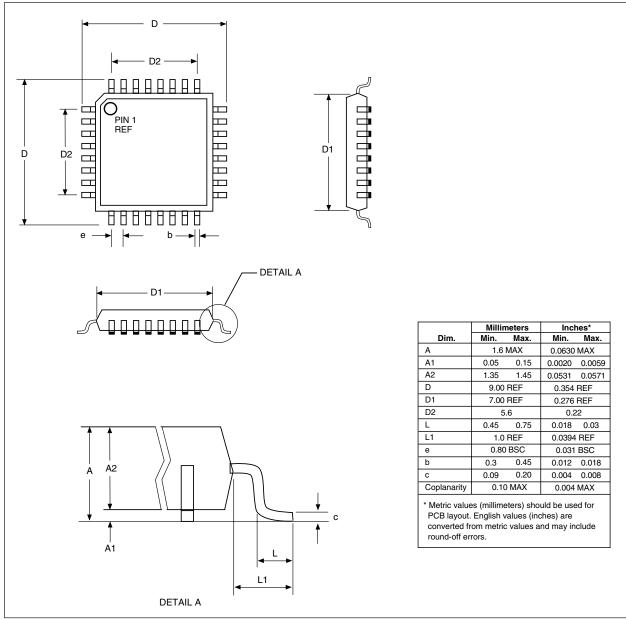

| Figure 4-1. Package Dimensions - 28-Pin TSSOP                  | 4-1  |

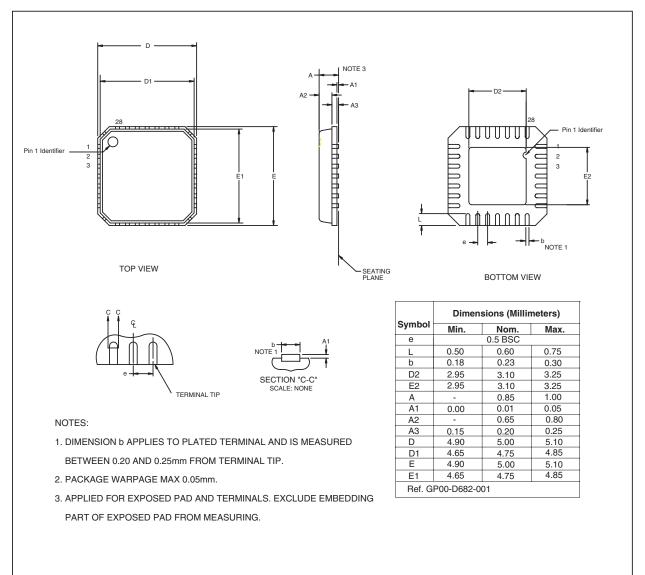

| Figure 4-2. Package Dimensions - 28-Pin QFN                    | 4-2  |

| Figure 4-3. Package Dimensions - 32-Pin LQFP                   | 4-3  |

## **Tables**

| Table 1-1. SCXV.22bis Modem Model/Order/Part Numbers             | 1-2  |

|------------------------------------------------------------------|------|

| Table 1-2. Default Countries Supported                           | 1-6  |

| Table 1-3. Supported AT Commands                                 | 1-8  |

| Table 2-1. +MS Command Automode Connectivity                     | 2-3  |

| Table 2-2. Supported Caller ID Types                             | 2-6  |

| Table 2-3. Select Low-Power Mode (-SLP) Command Comparison Table | 2-7  |

| Table 3-1. CX84100 V.22bis Modem 28-Pin TSSOP Pin Signals        | 3-3  |

| Table 3-2. CX84100 V.22bis Modem Pin Signal Definitions          | 3-4  |

| Table 3-3. CX84100 V.22bis Modem I/O Type Definitions            | 3-7  |

| Table 3-4. CX84100 V.22bis Modem DC Electrical Characteristics   | 3-7  |

| Table 3-5. CX20493 LSD 28-Pin QFN Pin Signals                    | 3-10 |

| Table 3-6. CX20493 LSD 28-Pin QFN Signal Definitions             | 3-11 |

| Table 3-7. CX20493 LSD 32-Pin LQFP Pin Signals                   | 3-15 |

| Table 3-8. CX20493 LSD 32-Pin LQFP Pin Signal Definitions        | 3-16 |

| Table 3-9. CX20493 LSD GPIO DC Electrical Characteristics        | 3-18 |

| Table 3-10. CX20493 LSD AVdd DC Electrical Characteristics       | 3-18 |

| Table 3-11. Operating Conditions                                 | 3-19 |

| Table 3-12. Absolute Maximum Ratings                             | 3-19 |

| Table 3-13. Current and Power Requirements                       | 3-20 |

| Table 3-14. Crystal Specifications                               | 3-22 |

|                                                                  |      |

## 1. Introduction

#### 1.1 Overview

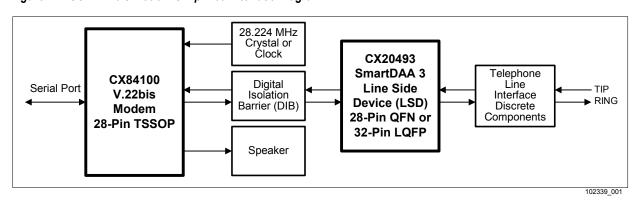

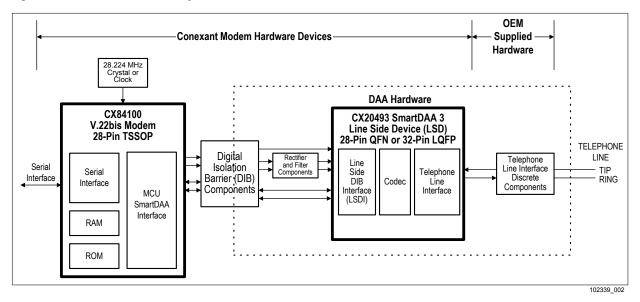

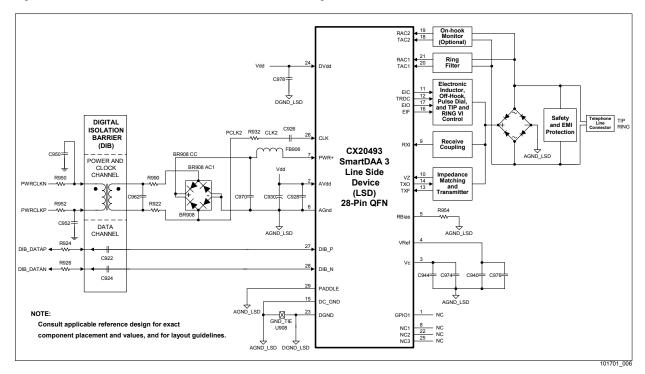

The Conexant® CX84100-41/-23 SCXV.22bis modem supports up to V.22bis data modem operation with V.42 and MNP 4 error correction and V.42 bis data compression over a serial host interface. Major hardware interfaces and signal interfaces are illustrated in Figure 1-1 and Figure 1-2, respectively.

Conexant's SmartDAA® technology (patent pending) eliminates the need for a costly analog transformer, relays, and opto-isolators typically used in discrete DAA implementation of country-specific modem configurations thereby reducing system solution cost to a single bill of materials (BOM).

The SmartDAA system-powered DAA operates reliably without drawing power from the line, unlike line-powered DAAs, which operate poorly when line current is insufficient due to long lines or poor line conditions. Enhanced features, such as monitoring of local extension status without going off-hook, are also supported.

Incorporating Conexant's proprietary Digital Isolation Barrier (DIB) design (patent pending) and other innovative DAA features, the SmartDAA architecture simplifies application design, minimizes layout area, and reduces component cost.

The SCXV.22bis Modem device set, consisting of a CX84100 V.22bis Modem in a 28-pin TSSOP package and a CX20493 SmartDAA Line Side Device (LSD) in either a 28-pin Quad Flat No-lead (QFN) package or a 32-pin Low Profile Quad Pack (LQFP) package, supports data operation with hardware-based modem controller, digital signal processing, and DAA/telephone line interface functions.

The CX84100 V.22bis Modem integrates microcontroller (MCU), serial host interface, ROM code, RAM, and SmartDAA system side device (SSD) functions onto a single die.

Small, low profile packages, low voltage operation, and low power consumption make this device set an ideal V.22bis solution for embedded applications.

Although the modem operates by executing a mask code from internal ROM and RAM, a country profile can be added or modified via host upload to the modem internal RAM.

In V.22 fast connect mode, the modem can connect at 1200 bps with a very short training time, which is very efficient for small data transfers. Also, V.80 synchronous access mode supports host-controlled communication protocols.

This data sheet describes the modem capabilities. Commands and parameters are defined in the Commands Reference Manual (Doc. No. 102338).

Table 1-1. SCXV.22bis Modem Model/Order/Part Numbers

| Model/Order/Part Numbers |                      |                                     |                                                     |  |

|--------------------------|----------------------|-------------------------------------|-----------------------------------------------------|--|

| Marketing Name           | Device Set Order No. | Modem<br>[28-Pin TSSOP]<br>Part No. | Line Side Device (LSD)<br>[28-Pin QFN]<br>Part No.  |  |

| SCXV22bis                | DS22-L100-041        | CX84100-41                          | CX20493-21                                          |  |

| SCXV22bis Pb Free        | DS22-L100-023        | CX84100-23                          | CX20493-31                                          |  |

| Marketing Name           | Device Set Order No. | Modem<br>[28-Pin TSSOP]<br>Part No. | Line Side Device (LSD)<br>[38-Pin LQFP]<br>Part No. |  |

| SCXV22bis                | DSCX-V22-041         | CX84100-41                          | CX20493-25                                          |  |

| SCXV22bis Pb Free        | DSCX-V22LF-023       | CX84100-23                          | CX20493-35                                          |  |

Figure 1-1. SCXV.22bis Modem Simplified Interface Diagram

Figure 1-2. SCXV.22bis Modem Major Interfaces

#### 1.2 Features

- Modulations

- ITU-T V.22bis (2400 bps)

- V.22 and Bell 212A (1200 bps)

- V.22 fast connect

- V.21 and Bell 103 (300 bps)

- V.23 1200/75 and 75/1200

- V.23 half duplex (1200 bps)

- Error correction and data compression

- V.42 (LAPM) error correction

- MNP2-MNP4 error correction

- V.42 bis data compression

- Serial interface

- Synchronous data mode

- Asynchronous data mode (normal and direct)

- 10- and 11-bit data

- DTE speeds up to 57600 bps

- AT Command speed sensing from 300 bps to 57600 bps

- RTS/CTS hardware flow control

- XON/XOFF software flow control

- AT Command Set

- Command set includes common Hayes/legacy and V.250 commands

- AT\$Fn fast connect commands

- Other Protocols

- V.80 Synchronous Access Mode

- V.23 Reverse Mode Protocol

- Caller ID (CID) decoding

- On-hook Caller ID Type I decoding

- FSK decoder for Bell 202/V.23

- Line reversal detection

- Call Waiting Caller ID (CWCID) Type II decoding

- DTMF generation

- Standard DTMF tone dialing generation

- Worldwide compliance

- Worldwide DC Mask compliance (DC1, DC2, DC3, and DC4)

- Worldwide pulse dialing

- Blacklisting

- Enhanced DAA features

- Digital Line Protection

- Line reversal detection (for U.K. Caller ID signaling)

- Line In Use detection

- Extension Pickup detection (option to automatically disconnect or inform the DTE)

- Remote Hang-up detection

- Thin packages support low profile designs (1.6 mm max. height)

- CX84100 V.22bis Modem in 28-pin TSSOP

- CX20493 Line Side Device in 28-pin QFN or 32-pin LQFP

- Power

- Single +3.3 V supply

- Low Power Mode

- Pin-compatible with Conexant SmartV.XX Modem (V.90+/V.34/V.32bis) in 28-pin CTLGA (see Doc. No. 102025)

#### 1.2.1 SmartDAA Features

- System side powered DAA operates under poor line current supply conditions

- Wake-on-ring

- Ring detection

- Line polarity reversal detection

- Line current loss detection

- Pulse dialing

- Line In Use detection detects even while on-hook

- Remote Hang-up detection for efficient call termination

- Extension Pickup detection

- Call Waiting detection

- Digital Line Protection

- Meets worldwide DC VI Masks requirements

#### 1.2.2 Applications

- Set top boxes

- Point-of-Sale terminals

- ATM machines

- Minitel terminals

#### 1.3 Technical Overview

#### 1.3.1 General Description

Modem operation, including dialing, call progress, telephone line interface, telephone handset interface, and host interface functions are supported and controlled through the AT command set.

The modem hardware connects to the host via a serial interface. The OEM adds a crystal circuit or clock input, DIB components, telephone line interface, and other supporting discrete components as required by the application to complete the system.

#### 1.3.2 MCU

The MCU performs processing of general modem control, command sets, data modem, error correction, worldwide, V.80, serial host interface functions, and signal processing.

#### 1.3.3 Operating Modes

#### 1.3.3.1 Data Modes

The modem operates in 2-wire full-duplex, asynchronous and synchronous modes at line rates up to 2400 bps (V.22bis), 1200 bps (V.22, V.22 fast connect, and Bell 212A), and 300 bps (V.21 and Bell 103). V.23 full duplex (asymmetrical connect rate of 1200 bps in one direction and 75 bps in the other direction) and V.23 half duplex mode (1200 bps) are also supported.

In V.22 fast connect data mode, the modem can connect at 1200 bps with a very short training time, which is very efficient for small data transfers.

#### 1.3.3.2 Worldwide Operation

The modem operates in TBR21-compliant and other countries. Country-dependent modem parameters for functions such as dialing, carrier transmit level, calling tone, call progress tone detection, answer tone detection, blacklisting, Caller ID, and relay control are programmable.

SmartDAA technology allows a single PCB design and single BOM to be homologated worldwide. Advanced features such as extension pickup detection, remote hang-up detection, line-in-use detection, and digital line detection are supported.

Internal ROM includes default profiles for 64 countries. Additional country profiles can be uploaded to internal RAM (request additional country profiles from a Conexant Sales Office). Duplicate country profiles uploaded to internal RAM will override the default profiles in internal firmware. Country code IDs are defined by ITU-TT.35. The default countries supported are listed in Table 1-2.

Table 1-2. Default Countries Supported

| Country        | Country Code | Country              | Country Code |

|----------------|--------------|----------------------|--------------|

| Argentina      | 7            | Luxembourg           | 69           |

| Australia      | 9            | Malaysia             | 6C           |

| Austria        | 0A           | Mexico               | 73           |

| Belgium        | 0F           | Morocco              | 77           |

| Brazil         | 16           | Netherlands          | 7B           |

| Bulgaria       | 1B           | New Zealand          | 7E           |

| Canada         | 20           | Norway               | 82           |

| Chile          | 25           | Pakistan             | 84           |

| China          | 26           | Philippines          | 89           |

| Columbia       | 27           | Poland               | 8A           |

| Croatia        | FA           | Portugal             | 8B           |

| Cyprus         | 2D           | Romania              | 8E           |

| Czech Republic | 2E           | Russia               | B8           |

| Denmark        | 31           | South Africa         | 9F           |

| Egypt          | 36           | Saudi Arabia         | 98           |

| Estonia        | F9           | Senegal              | 99           |

| Finland        | 3C           | Singapore            | 9C           |

| France         | 3D           | Slovakia             | FB           |

| Germany        | 42           | Slovenia             | FC           |

| Greece         | 46           | Spain                | A0           |

| Hong Kong      | 50           | Sri Lanka            | A1           |

| Hungary        | 51           | Sweden               | A5           |

| Iceland        | 52           | Switzerland          | A6           |

| India          | 53           | Taiwan               | FE           |

| Indonesia      | 54           | Thailand             | A9           |

| Ireland        | 57           | Tunisia              | AD           |

| Israel         | 58           | Turkey               | AE           |

| Italy          | 59           | UK                   | B4           |

| Japan          | 0            | UK Genesys           | FD           |

| Korea          | 61           | United Arab Emirates | B3           |

| Kuwait         | 62           | Uruguay              | B7           |

| Lebanon        | 64           | USA                  | B5           |

## 1.3.4 Reference Design

An RS-232 external data modem reference design is available to minimize application design time, reduce development cost, and accelerate market entry.

A design package is available in electronic form. This package includes schematics, bill of materials (BOM), vendor part list (VPL), board layout files in Gerber format, and complete documentation.

## 1.4 Hardware Description

SmartDAA™ technology (patent pending) eliminates the need for a costly analog transformer, relays, and opto-isolators that are typically used in discrete DAA implementations. The programmable SmartDAA architecture simplifies product implementation in worldwide markets by eliminating the need for country-specific components.

#### 1.4.1 CX84100 V.22bis Modem

The CX84100 V.22bis Modem, packaged in a 28-pin TSSOP, includes a Microcontroller (MCU), internal ROM code, internal RAM, and SmartDAA interface functions.

The modem connects to the host via a logical V.24 (EIA/TIA-232-E) serial DTE interface.

The modem performs the command processing and host interface functions. The crystal or clock input frequency is 28.224 MHz.

The modem performs telephone line signal modulation/demodulation in a hardware digital signal processor (DSP) which reduces computational load on the host processor.

The SmartDAA Interface communicates with, and supplies power and clock to, the LSD through the DIB.

#### 1.4.2 Digital Isolation Barrier

The OEM-supplied Digital Isolation Barrier (DIB) electrically DC isolates the CX84100 V.22bis Modem from the CX20493 LSD and telephone line. The CX84100 V.22bis Modem is connected to a fixed digital ground and operates with standard CMOS logic levels. The LSD is connected to a floating ground and can tolerate high voltage input (compatible with telephone line and typical surge requirements).

The DIB transformer couples power and clock from the CX84100 V.22bis Modem to the CX20493 LSD.

The DIB data channel supports bidirectional half-duplex serial transfer of data, control, and status information between the CX84100 V.22bis Modem and the CX20493 LSD over two lines.

#### 1.4.3 CX20493 SmartDAA Line Side Device

The CX20493 SmartDAA Line Side Device (LSD) includes a Line Side DIB Interface (LSDI), a coder/decoder (codec), and a Telephone Line Interface (TLI).

The LSDI communicates with, and receives power and clock from, the SmartDAA interface in the CX84100 V.22bis Modem through the DIB.

LSD power is received from the CX84100 PWRCLKP and PWRCLKN pins via the DIB through a half-wave rectifying diode and capacitive power filter circuit connected to the DIB transformer secondary winding.

The CLK input is also accepted from the DIB transformer secondary winding through a capacitor and a resistor in series.

Information is transferred between the CX20493 LSD and the CX84100 V.22bis Modem through the DIB\_P and DIB\_N pins. These pins connect to the CX84100 V.22bis Modem DIB DATAP and DIB DATAN pins, respectively, through the DIB.

The TLI integrates DAA and direct telephone line interface functions and connects directly to the line TIP and RING pins, as well as to external line protection components.

Direct LSD connection to TIP and RING allows real-time measurement of telephone line parameters, such as the telephone central office (CO) battery voltage, individual telephone line (copper wire) resistance, and allows dynamic regulation of the off-hook TIP and RING voltage and total current drawn from the central office (CO). This allows the modem to maintain compliance with U.S. and worldwide regulations and to actively control the DAA power dissipation.

#### 1.5 Commands

Modem functions operate in response to data modem and V.80 AT commands and S Register parameters (Table 1-3). See AT Commands for CX84100-41/-23 SCXV.22bis Modem Reference Guide (Doc. No. 102338) for a complete description of the commands and registers.

Table 1-3. Supported AT Commands

| Command | Description                                          |  |

|---------|------------------------------------------------------|--|

| \$F     | FastConnect Control                                  |  |

| %C      | Enable/Disable Data Compression                      |  |

| %E      | Enable/Disable Line Quality Monitor and Auto-Retrain |  |

| %L      | Report Line Signal Level                             |  |

| %Q      | Report Line Signal Quality                           |  |

| %TT     | PTT Test Command                                     |  |

| &C      | RLSD Option                                          |  |

| &D      | DTR Option                                           |  |

| &F      | Restore Factory Configuration (Profile)              |  |

| &G      | Select Guard Tone                                    |  |

| &K      | Flow Control                                         |  |

| &M      | Asynchronous/Synchronous Mode Selection              |  |

| &P      | Select Pulse Dial Make/Break Ratio                   |  |

| &Q      | Sync/Async Mode                                      |  |

| &R      | RTS/CTS Option                                       |  |

| &T      | Local Analog Loopback Test                           |  |

| &V      | Display Current Configuration and Stored Profiles    |  |

| &V1     | Display Last Connection Statistics                   |  |

| &X      | Select Synchronous Clock Source                      |  |

| **      | Load to Internal RAM                                 |  |

| *B      | Display Blacklisted Numbers                          |  |

| *D      | Display Delayed Numbers                              |  |

| \A      | Select Maximum MNP Block Size                        |  |

| \G      | Modem-to-Modem Flow Control (XON/XOFF)               |  |

| \N      | Operating Mode                                       |  |

| \V      | Single Line Connect Message Enable                   |  |

Table 1-3. Supported AT Commands (Continued)

| Command | Description                                   |  |

|---------|-----------------------------------------------|--|

| +DR     | Data Compression Reporting                    |  |

| +DS     | Data Compression                              |  |

| +ER     | Error Control Reporting                       |  |

| +ES     | Error Control and Synchronous Mode Selection  |  |

| +ESA    | Configure Synchronous Access Submode          |  |

| +ESR    | Selective Repeat                              |  |

| +ETBM   | Call Termination Buffer Management            |  |

| +GCI    | Country of Installation                       |  |

| +IBC    | In-Band Commands                              |  |

| +IFC    | DTE Modem Local Flow Control                  |  |

| +ITF    | Transmit Flow Control Thresholds              |  |

| +MR     | Modulation Reporting Control                  |  |

| +MS     | Modulation Selection                          |  |

| +PCW    | Call Waiting Enable                           |  |

| +VCID   | Caller ID (CID)                               |  |

| +VDR    | Distinctive Ring                              |  |

| +VDT    | Control Tone Cadence Reporting                |  |

| +VRID   | Report Retrieved CID                          |  |

| -HTRV   | History of Tip and Ring Voltage               |  |

| -SLP    | Select Low-Power Mode                         |  |

| -STE    | Set Telephony Extension                       |  |

| -TRV    | Tip and Ring Voltage Measurement              |  |

| -TTE    | Threshold Adjustments for Telephony Extension |  |

| A       | Answer                                        |  |

| В       | ITU-T or Bell                                 |  |

| D       | Dial                                          |  |

| E       | Command Echo                                  |  |

| Н       | Disconnect (Hang-Up)                          |  |

| 1       | Identification                                |  |

| L       | Speaker Volume                                |  |

| M       | Speaker Control                               |  |

| 0       | Return to On-Line Data Mode                   |  |

| Р       | Set Pulse Dial Default                        |  |

| Q       | Quiet Results Codes Control                   |  |

| S       | Read/Write S-Parameter                        |  |

| Т       | Set Tone Dial Default                         |  |

| V       | Result Code Form                              |  |

| W       | Connect Message Control                       |  |

| Х       | Extended Result Codes                         |  |

| Z       | Soft Reset and Restore Profiles               |  |

## 2. Technical Specifications

## 2.1 Serial DTE Interface Operation

## 2.1.1 Automatic Speed/Format Sensing

**Command Mode and Data Modem Mode.** The modem can automatically determine the speed and format of the data sent from the DTE. The modem can sense speeds of 300, 600, 1200, 2400, 4800, 7200, 9600, 12000, 14400, 16800, 19200, 28800, 38400, and 57600 bps and the following data formats:

| Parity | Data Length (No. of Bits) | No. of<br>Stop Bits | Character Length (No. of Bits) |

|--------|---------------------------|---------------------|--------------------------------|

| None   | 7                         | 2                   | 10                             |

| Odd    | 7                         | 1                   | 10                             |

| Even   | 7                         | 1                   | 10                             |

| None   | 8                         | 1                   | 10                             |

| Odd    | 8                         | 1                   | 11*                            |

| Even   | 8                         | 1                   | 11*                            |

<sup>\*11-</sup>bit characters are sensed, but the parity bit is stripped off during data transmission in Normal and Error Correction modes.

The modem can speed sense data with mark or space parity and configures itself as follows:

| DTE Configuration | Modem Configuration |  |

|-------------------|---------------------|--|

| 7 mark            | 7 none              |  |

| 7 space           | 8 none              |  |

| 8 mark            | 8 none              |  |

| 8 space           | 8 even              |  |

## 2.2 Establishing Data Modem Connections

### 2.2.1 Dialing

**Pulse Dialing.** Pulse dialing is supported in accordance with EIA/TIA-496-A.

**Blind Dialing.** The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

## 2.2.2 Modem Handshaking Protocol

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

#### 2.2.3 Call Progress Tone Detection

Ringback, equipment busy, congested tone, warble tone, and progress tones can be detected in accordance with the applicable standard.

#### 2.2.4 Answer Tone Detection

Answer tone can be detected over the frequency range of  $2100 \pm 40$  Hz in ITU-T modes and  $2225 \pm 40$  Hz in Bell modes.

#### 2.2.5 Ring Detection

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

### 2.2.6 Billing Protection

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds to allow transmission of the billing tone signal.

### 2.2.7 Connection Speeds

Line connection can be selected using the +MS command. The +MS command selects modulation, enables/disables automode, and selects minimum and maximum line speeds (Table 2-1).

#### 2.2.8 Automode

Automode detection can be enabled by the +MS command to allow the modem to connect to a remote modem (Table 2-1).

Table 2-1. +MS Command Automode Connectivity

| <mod></mod> | Modulation | Possible Rates (bps) <sup>1</sup> | Notes      |

|-------------|------------|-----------------------------------|------------|

| V21         | V.21       | 300                               |            |

| V22         | V.22       | 1200                              |            |

| V22B        | V.22bis    | 2400 or 1200                      | Default    |

| V23C        | V.23       | 1200                              | See Note 2 |

| B103        | Bell 103   | 300                               |            |

| B212        | Bell 212   | 1200                              |            |

#### Notes:

- See optional <automode>, <min\_rate>, and <max\_rate> subparameters for the +MS command.

- For V.23, originating modes transmit at 75 bps and receive at 1200 bps; answering modes transmit at 1200 bps and receive at 75 bps. The rate is always specified as 1200 bps. V.23 half duplex is not supported.

- 3. If the DTE speed is set to less than the maximum supported DCE speed in automode, the maximum connection speed is limited to the DTE speed.

#### 2.3 Data Mode

Data mode exists when a telephone line connection has been established between modems and all handshaking has been completed.

## 2.3.1 Speed Buffering (Normal Mode)

Speed buffering allows a DTE to send data to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

#### 2.3.2 Flow Control

**DTE-to-Modem Flow Control.** If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control with the DTE to ensure data integrity.

#### 2.3.3 Direct Mode

The Direct mode allows data to be transmitted and received directly from either the DTE or remote modem. The Direct mode is selected with the AT&Q0 or AT\N1 command.

When running Direct mode, no flow control characters are recognized or transmitted, and the modem cannot perform error correction. The purpose of the Direct mode is to make the modem 'dumb' for compatibility with older style modems.

Any data received while the modem is in command mode is lost.

#### 2.3.4 Escape Sequence Detection

The +++ escape sequence can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by an S2 Register value greater than 127.

#### 2.3.5 Telephone Line Monitoring

**Loss of Carrier.** If carrier is lost for a time greater than specified by the S10 register, the modern disconnects

#### 2.3.6 Retrain

The modem may lose synchronization with the received line signal under poor or changing line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved, or until 30 seconds elapse resulting in line disconnect.

#### 2.3.7 Programmable Inactivity Timer

The modem disconnects from the line if data is not sent or received for a specified length of time. In normal or error-correction mode, this inactivity timer is reset when data is received from either the DTE or from the line. This timer can be set to a value between 0 and 255 seconds by using register S30. A value of 0 disables the inactivity timer.

### 2.3.8 DTE Signal Monitoring (Serial DTE Interface Only)

**DTR#.** When DTR# is asserted, the modem responds in accordance with the &Dn and &On commands.

RTS#. RTS# is used for flow control if enabled by the &K command in normal or error-correction mode.

## 2.4 Error Correction and Data Compression

#### 2.4.1 V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as a fallback, MNP 4. The modem provides a detection and negotiation technique for determining and establishing the best method of error correction between two modems.

#### 2.4.2 MNP 2-4 Error Correction

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. Supporting stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

#### 2.4.3 V.42 bis Data Compression

V.42 bis data compression mode, enabled by the %Cn command or S46 register, operates when a LAPM or MNP 2-4 connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two 512-byte dictionaries are used to store the strings. These dictionaries are dynamically updated during normal operation.

## 2.5 Telephony Extensions

The following telephony extension features are supported that can typically be implemented in designs for set-top box applications to enhance end-user experience:

- Line In Use detection

- Extension Pickup detection

- Remote Hang-up detection

- Digital Line Protection

#### 2.5.1 Line In Use Detection

The Line In Use Detection feature can stop the modem from disturbing the phone line when the line is already being used. When an automated system tries to dial using ATDT and the phone line is in use, the modem will not go off hook and will respond with the message "LINE IN USE".

#### 2.5.2 Extension Pickup Detection

The Extension Pickup Detection feature (also commonly referred as PPD or Parallel phone detection) allows the modem to detect when another telephony device (i.e., fax machine, phone, satellite/cable box) is attempting to use the phone line.

This feature can be used to quickly drop a modem connection in the event when a user picks up a extension phone line. For example, this feature allows set top boxes with an integrated SCXV.22bis Modem to give normal voice users the highest priority over the telephone line.

## 2.5.3 Remote Hangup Detection

The Remote Hangup Detection feature will cause the modem to go back onhook during a data connection when the remote modem is disconnected for abnormal termination reasons (remote phone line unplugged, remote server/modem shutdown.

## 2.5.4 Digital Line Protection

The Digital Line Protection (DLP) feature prevents damage to the modem if a digital PBX telephone line is detected. This is accomplished by forcing the modem to go back on hook if it attempts to go off hook on a digital line. This feature is enabled by default and can be tuned via the -TTE command.

The SmartDAA qualifies the line current and power rating every time the modem goes off hook and decides with a given threshold to qualify the presence of a digital PBX line.

#### 2.6 Caller ID

Both Type I Caller ID (On-Hook Caller ID) and Type II Caller ID (Call Waiting Caller ID) are supported for U.S. and many other countries (see Section 2.7). Both types of Caller ID are enabled/disabled using the +VCID command. When enabled, Caller ID information (date, time, caller code, and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current Caller ID mode and mode capabilities of the modem to be retrieved from the modem. Table 2-2 identifies Caller ID type differences.

Table 2-2. Supported Caller ID Types

| Caller ID Type             | Modem State | Parallel Phone |

|----------------------------|-------------|----------------|

| Type I CID (On-hook)       | On-hook     | On-hook        |

| Type II CID (Call Waiting) | Off-hook    | On-hook        |

#### 2.6.1 Type II CID

When connected in V.22bis and Call Waiting is detected (assuming Call Waiting detection is enabled by +PCW = 0 command), the modem notifies the user of incoming call by toggling the RI pin. Under similar condition except +PCW = 1, the modem will hang up. In all other modulations, when  $+PCW = \{0 \text{ or } 1\}$  and Call Waiting comes in during data mode, the modem will hang up.

When +PCW = 1 and Caller ID is enabled, the modem will attempt to do Type II Caller ID before hanging up. The Caller ID information may then be retrieved by issuing  $+VRID = \{0 \text{ or } 1\}$  after the modem hangs up.

The modem operates as normal when Call Waiting detection is disabled (+PCW = 2). However, the modem may also disconnect due to a carrier loss caused by the noise disturbance that the Call Waiting introduced to the line.

## 2.7 Worldwide Country Support

Internal modem firmware supports 64 country profiles (see Section 1.3.3.2). A country profile can be uploaded via SRAM patch in addition to, or to override, one of the default countries in the code. These country profiles include the following country-dependent parameters:

- Dial tone detection levels and frequency ranges.

- Pulse dialing parameters: make/break times, set/clear times, and dial codes.

- Ring detection frequency range.

- Type I and Type II Caller ID are supported for many countries. Consult firmware release notes for a list of the supported countries and the criteria for additional country support.

- Blind dialing enabled/disable.

- Calling tone is generated in accordance with V.25. Calling tone may be toggled (enabled/disabled) by inclusion of a "^" character in a dial string. It may also be disabled.

- Frequency and cadence of tones for busy, ringback, congested, warble, dial tone 1, and dial tone 2.

- Answer tone detection period.

Blacklist parameters. The modem can operate in accordance with requirements of

individual countries to prevent misuse of the network by limiting repeated calls to

the same number when previous call attempts have failed. Call failure can be

detected for reasons such as no dial tone, number busy, no answer, no ringback

detected, voice (rather than modem) detected, and key abort (dial attempt aborted by

user). Actions resulting from such failures can include specification of minimum

inter-call delay, extended delay between calls, and maximum numbers of retries

before the number is permanently forbidden ("blacklisted").

Country profiles may be altered or customized by modifying the country-dependent parameters. Additional profiles may also be included by uploading to internal RAM. Contact the local Conexant sales office if country code customization is required.

## 2.8 Diagnostics

#### 2.8.1 Commanded Tests

Diagnostics are performed in response to &T commands.

**Analog Loopback (&T1 Command).** Data from the local DTE is sent to the modem, which loops the data back to the local DTE.

#### 2.9 Low Power Mode

The S24 register sets the length of time, in seconds, that the modem will operate in normal mode with no detected telephone line or DTE line activity before entering low-power mode. The timer resets upon any DTE line or telephone line activity. Neither DTE line nor telephone inactivity will cause the modem to enter into low-power mode if the S24 is set to zero.

When the S24 timer expires, the modem enters into low-power mode, which has three variations controlled by –SLP or Select Low-Power Mode command. The low-power mode can be configured either in idle, sleep, or stop mode as shown in Table 2-3. Either a ring input or host serial transmit activity will force the modem out of low-power mode and back to normal mode. Note that the first issued command will get processed during idle mode but not in sleep or stop mode. The first byte sent merely wakes up the modem, thus missing the first command. However, subsequent commands will get processed as normal operating mode resumes.

The device power consumption, which includes the LSD or CX20493, is listed in Table 3-13.

Table 2-3. Select Low-Power Mode (-SLP) Command Comparison Table

| AT-SLP =                                  | 0 (Idle)             | 1 (Sleep)           | 2 (Stop) |  |  |

|-------------------------------------------|----------------------|---------------------|----------|--|--|

| Ring input                                | Yes                  | Yes                 | Yes      |  |  |

| Host serial TXD activity  Yes  Yes*  Yes* |                      |                     |          |  |  |

| * The first AT command is ignored bu      | t modem returns to n | ormal operating mod | e.       |  |  |

## 3. Hardware Interface

## 3.1 CX84100 V.22bis Modem Hardware Pins and Signals

### 3.1.1 CX84100 V.22bis Modem Signal Summary

#### 3.1.1.1 CX20493 LSD Interface (Through DIB)

The DIB interface signals are:

- Clock and Power Positive (PWRCLKP); output

- Clock and Power Negative (PWRCLKN); output

- Data Positive (DIB DATAP); input/output

- Data Negative (DIB DATAN); input/output

#### 3.1.1.2 Call Progress Speaker Interface

The call progress speaker interface signal is:

• Digital speaker output (DSPKOUT); output

#### 3.1.1.3 Serial DTE Interface and Indicator Outputs

The supported serial host interface signals are:

- Serial Transmit Data: TXD#; input

- Serial Receive Data: RXD#; output

- Clear to Send: CTS#; output

- Received Signal Line Detected: RLSD#; output

- Request to Send: RTS#, input

- Ring Indicator: RI#, output

Additional clock signals provided for synchronous mode are:

- Receive Data Clock: RDCLK#

- Transmit Data Clock: TDCLK#

#### 3.1.1.4 Control and Signals

The supported control signals are:

- Reset: RESET#; input

- Low Power Oscillator Select; LPO; input

#### 3.1.1.5 **Crystal/Clock and Power Signals**

Figure 3-1. CX84100 V.22bis Modem Hardware Interface Signals

TXD#

RXD#

CTS#

RI#

DTR#

RTS#

+3.3V

NC

RLSD#

SERIAL DTE

INTERFACE

28.224 MHZ CRYSTAL

ALTERNATIVE INTERFACE 28.224 MHZ CLOCK

Supported crystal and power signals are:

Crystal/Clock input: XTLI Crystal return: XTLO +3.3 V power: VDD Ground; GND

#### 3.1.2 **CX84100 V.22bis Modem Pin Assignments and Signal Definitions**

CX84100 V.22bis Modem 28-pin TSSOP hardware interface signals for serial interface are shown by major interface in Figure 3-1, are shown by pin number in Figure 3-2, and are listed by pin number in Table 3-1.

CX84100 V.22bis Modem hardware interface signals for serial interface are defined in Table 3-2.

I/O types are defined in Table 3-3. DC electrical characteristics are listed in Table 3-4.

VDD VDD\_CORE 22 VDD RESET CIRCUIT RESET# **PWRCLKP PWRCLKN** DIB\_DATAP

TXD#

RXD#

CTS#

RLSD#

RI#

DTR#

RTS# TDCLK#

XTLI

XTLO

LPO

9 GND GND

RDCLK# XTLI

18

NC

240K

CX84100 RESERVED V.22bis Modem RESERVED 28-Pin TSSOP NC RESERVED RESERVED RESERVED

DIB DATAN

DSPKOUT

102339\_003

DIGITAL ISOLATION

BARRIER (DIB)

SPEAKER CIRCUIT

**DSPKOUT** XTLI 28 € XTLO 27 CI 2 **PWRCLKN** RESET# **PWRCLKP** RXD# 25 € GND TXD# 24 C... VDD\_CORE RDCLK# 6 23 € LPO 22 C. VDD VDD TDCLK# 21 CII DIB\_DATAN CX84100 GND <u>...</u> 9 20 € DIB\_DATAP 19 € RTS# **RESERVED** CTS# 18 € RI# 17 C DTR# 12 RLSD# RESERVED RESERVED 13 16 C RESERVED 15 € **RESERVED** 14 Top View

Figure 3-2. CX84100 V.22bis Modem 28-Pin TSSOP Pin Signals

102339\_004

Table 3-1. CX84100 V.22bis Modem 28-Pin TSSOP Pin Signals

| Pin No. | Signal Name | Pin No. | Signal Name |

|---------|-------------|---------|-------------|

| 1       | XTLI        | 15      | RESERVED    |

| 2       | XTLO        | 16      | RESERVED    |

| 3       | RESET#      | 17      | RLSD#       |

| 4       | RXD#        | 18      | RI#         |

| 5       | TXD#        | 19      | RESERVED    |

| 6       | RDCLK#      | 20      | DIB_DATAP   |

| 7       | VDD         | 21      | DIB_DATAN   |

| 8       | TDCLK#      | 22      | VDD         |

| 9       | GND         | 23      | LPO         |

| 10      | RTS#        | 24      | VDD_CORE    |

| 11      | CTS#        | 25      | GND         |

| 12      | DTR#        | 26      | PWRCLKP     |

| 13      | RESERVED    | 27      | PWRCLKN     |

| 14      | RESERVED    | 28      | DSPKOUT     |

Table 3-2. CX84100 V.22bis Modem Pin Signal Definitions

| Label     | Pin                      | I/O | I/O Type | Signal Name/Description                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------|--------------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           | System                   |     |          |                                                                                                                                                                                                                                                                                                                                              |  |  |

| XTLI      | 1                        | I   | lx       | 28.224 MHz Crystal Oscillator Input. Crystal oscillator input or external input pin. When using a crystal oscillator, connect the crystal between pins 1 and 2. If a crystal is not used, connect this pin to an external clock through a 100 pF capacitor (see Figure 3-1).                                                                 |  |  |

| XTLO      | 2                        | 0   | Ox       | <b>28.224 MHz Crystal Oscillator Output.</b> When using a crystal oscillator, connect the crystal between pins 1 and 2. This pin is left unconnected when an alternative clock source is applied to XTLI.                                                                                                                                    |  |  |

| RESET#    | 3                        | I   | Itpu     | Master Reset. The RESET# input resets the CX84100 device and returns the modem to the factory default values.                                                                                                                                                                                                                                |  |  |

|           |                          |     |          | When RESET# is at logic 0, it holds the modem in the reset state; A low-to-high transition releases the modem from the reset state. After application of VDD, RESET# must be held low for at least 15 ms after the VDD power reaches operating range. The modem device set is ready to use 25 ms after the low-to-high transition of RESET#. |  |  |

|           |                          |     |          | The RESET# input is typically connected to a reset switch circuit.                                                                                                                                                                                                                                                                           |  |  |

| VDD       | 7, 22                    | Р   | PWR      | Digital Supply Voltage. Connect to +3.3 V.                                                                                                                                                                                                                                                                                                   |  |  |

| VDD_CORE  | 24                       | P   | PWR      | Core Voltage. Core Voltage. Internal +1.8 V core voltage for decoupling. Do not connect this pin to an external +1.8 V power supply.                                                                                                                                                                                                         |  |  |

| GND       | 9, 25                    | G   | GND      | Digital Ground. Connect to system ground.                                                                                                                                                                                                                                                                                                    |  |  |

| LPO       | 23                       | I   | Rx       | Low Power Oscillator. Connect to +3.3 V through a 240 kΩ ±1% resistor. This enables an internal oscillator to generate a 33 MHz clock for use in low power modes.                                                                                                                                                                            |  |  |

| RESERVED  | 13, 14,<br>15, 16,<br>19 |     |          | Reserved. Connected to internal circuitry. Leave open.                                                                                                                                                                                                                                                                                       |  |  |

|           |                          |     | Speak    | er Interface                                                                                                                                                                                                                                                                                                                                 |  |  |

| DSPKOUT   | 28                       | 0   | Ot2      | Speaker Digital Output. This signal is the digital output made from the received analog input signal digitized to TTL levels by an internal comparator.                                                                                                                                                                                      |  |  |

|           | •                        |     | DIB      | Interface                                                                                                                                                                                                                                                                                                                                    |  |  |

| PWRCLKP   | 26                       | 0   | It/Odpc  | Clock and Power Positive. Provides clock and power to the LSD. Connect to DIB transformer primary winding non-dotted terminal.                                                                                                                                                                                                               |  |  |

| PWRCLKN   | 27                       | 0   | lt/Odpc  | Clock and Power Negative. Provides clock and power to the LSD. Connect to DIB transformer primary winding dotted terminal.                                                                                                                                                                                                                   |  |  |

| DIB_DATAP | 20                       | I/O | ldd/Odd  | <b>Data Positive.</b> Transfers data, control, and status information between the CX84100 V.22bis Modem and the LSD. Connect to LSD through DIB data positive channel components.                                                                                                                                                            |  |  |

| DIB_DATAN | 21                       | 1/0 | ldd/Odd  | <b>Data Negative.</b> Transfers data, control, and status information between the CX84100 V.22bis Modem and the LSD. Connect to LSD through DIB data negative channel components.                                                                                                                                                            |  |  |

Table 3-2. CX84100 V.22bis Modem Pin Signal Definitions (Continued)

| Label | Pin | I/O | I/O Type        | Signal Name/Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|-----|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     | V.2 | 4 (EIA/TIA-232- | E) DTE Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                      |

| TXD#  | 5   | 1   | Itpu/Ot2        | Transmit Serial Input (EIA BA/ITU-T CT103). Serial data is sent on this line from the DTE to the DCE. The DTE holds this line at logic 1 when no data is being transmitted. The following signals must be at logic 0, where implemented, before data can be transmitted on this line: Request To Send (RTS), Clear To Send (CTS), and Data Terminal Ready (DTR).                                                             |

| RXD#  | 4   | 0   | It/Ot2          | Receive Serial Output (EIA BB/ITU-T CT104). Serial data is sent on this line from the DCE to the DTE. This pin is held at logic 1 (Mark) when no data is being transmitted, and is held logic 1 for a brief interval after a logic 0 to 1 transition on the Request To Send line (RTS), in order to allow the transmission to complete.                                                                                      |

| CTS#  | 11  | 0   | Itpu/Ot2        | Clear To Send (EIA CB/ITU-T CT106). An answer signal to the DTE. When this signal is active, it tells the DTE that it can now start transmitting. When CTS is logic 0 and the Request To Send (RTS) and Data Terminal Ready (DTR) are both logic 0, the DTE is assured that its data will be sent to the communications link. Logic 1 indicates to the DTE that the DCE is not ready, and therefore data should not be sent. |

|       |     |     |                 | In asynchronous operation, in error correction or normal mode, CTS is always at logic 0 unless RTS/CTS flow control is selected by the &Kn command.                                                                                                                                                                                                                                                                          |

|       |     |     |                 | In synchronous operation, the modem also holds CTS at logic 0 during asynchronous command state. The modem switches CTS to logic 1 immediately upon going off-hook and holds it there until RLSD is at logic 0 in which case the modem is ready to transmit and receive synchronous data. CTS can also track the state of RTS via the &Rn command.                                                                           |

| RLSD# | 17  | 0   | It/Ot2          | Received Line Signal Detector (EIA CF/ITU-T CT109). The DCE uses this line to signal the DTE that a good signal is being received assuming AT&C0 command is not in effect (a "good signal" means a good analog carrier, that can ensure demodulation of received data).                                                                                                                                                      |

| RI#   | 18  | 0   | It/Ot2          | Ring Indicator (EIA CE/ITU-T CT125). On this line the DCE signals the DTE that there is an incoming call. This signal is maintained at logic 1 at all times except when the DCE receives a ringing signal.                                                                                                                                                                                                                   |

| DTR#  | 12  | 1   | Itpu/Ot2        | Data Terminal Ready (EIA CD/ITU-T CT108). When at logic 0, DTR# tells the DCE that the DTE is available for receiving. The DTR signal deals with the readiness of the equipment, as opposed to the Clear To Send (CTS) and Request To Send (RTS) signals that deal with the readiness of the communication channel.                                                                                                          |

|       |     |     |                 | Logic 1 places the modem in the disconnect state under the control of &Dn and &Qn commands.                                                                                                                                                                                                                                                                                                                                  |

Table 3-2. CX84100 V.22bis Modem Pin Signal Definitions (Continued)

| Label                                                 | Pin                       | I/O | I/O Type | Signal Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-------------------------------------------------------|---------------------------|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V.24 (EIA/TIA-232-E) DTE Serial Interface (Continued) |                           |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RTS#                                                  | 10                        | I   | Itpu/Ot2 | Request To Send (EIA CA/ITU-T CT105). The DTE uses this signal when it wants to transmit to the DCE. This signal, in combination with the Clear To Send (CTS) signal, coordinates data transmission between the DTE and the DCE.                                                                                                                                                                                                                        |  |  |

|                                                       |                           |     |          | A logic 0 on this line keeps the DCE in transmit mode. The DCE will receive data from the DTE to be forwarded to the communication link.                                                                                                                                                                                                                                                                                                                |  |  |

|                                                       |                           |     |          | The RTS and CTS signals relate to a half-duplex telephone line. A half duplex line is capable of carrying signals on both directions but only one at a time. When the DTE has data to send, it raises RTS, and then waits until the DCE changes from receive to transmit mode. The logic 1 to 0 transition of the RTS instructs the DCE to switch to "transmit" mode, and when a transmission is possible, the DCE sets CTS and transmission can begin. |  |  |

|                                                       |                           |     |          | On a full duplex line, like a hard-wired connection, where transmission and reception can occur simultaneously, the CTS and RTS signals are held to a constant logic 0 level. A logic 0 to 1 transition of the RTS instructs the DCE to complete data transmission and to switch to a "receive" (or "no transmission") mode.                                                                                                                            |  |  |

| TDCLK#                                                | 8                         | 0   | It/Ot2   | <b>Transmit Serial Clock</b> . The DCE sends the DTE a clock signal on this line. This enables the DTE to transmit serial data on the Transmitted Data line (TXD). The clock frequency is the same as the bit rate (±0.01%) of TXD with a duty cycle of 50±1%.                                                                                                                                                                                          |  |  |

|                                                       |                           |     |          | TDCLK# signal transition from logic 0 to 1 marks the center of each bit on TXD. Leave open if not used.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RDCLK#                                                | 6                         | 0   | lt/Ot2   | Receive Serial Clock. The DCE sends the DTE a clock signal on this line. RDCLK clocks the reception circuitry of the DTE, which receives serial data on the Received Data line (RXD). The clock frequency is the same as the bit rate (±0.01%) of RXD with a duty cycle of 50±1%. RDCLK# signal transition from logic 0 to 1 indicates the center of each signal bit on RXD. Leave open if not used.                                                    |  |  |

| Notes:                                                |                           |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| I/O Types: See Table 3-3                              | I/O Types: See Table 3-3. |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

3-6 **Conexant** 102339C

Table 3-3. CX84100 V.22bis Modem I/O Type Definitions

| I/O Type | Description                                                                            |

|----------|----------------------------------------------------------------------------------------|

| lx       | Input, wire                                                                            |

| Ox       | Output, wire                                                                           |

| Rx       | Oscillator pad, place 1%, 240 k $\Omega$ resistor from pad to VDD                      |

| lt/Ot2   | Digital input, +5 V tolerant, keeper/Digital output, 2 mA                              |

| Itpu/Ot2 | Digital input, +5 V tolerant, 75 kΩ pull up/Digital output, 2 mA                       |

| Itpu     | Digital input, + tolerant, 75 kΩ pull up                                               |

| Ot2      | Digital output, 2 mA                                                                   |

| lt/Odpc  | Digital input, +5 V tolerant/Digital output with adjustable drive; DIB clock and power |

| ldd/Odd  | Digital input/Digital output; DIB data transceiver                                     |

| PWR      | Power                                                                                  |

| GND      | Ground                                                                                 |

| MOTEO    |                                                                                        |

#### NOTES:

- 1. See DC characteristics in Table 3-4.

- 2. I/O Type corresponds to the device Pad Type. The I/O column in signal interface tables refers to signal I/O direction used in the application.

Table 3-4. CX84100 V.22bis Modem DC Electrical Characteristics

| Parameter                                                                                               | Symbol | Min.      | Тур. | Max.     | Units | Test Conditions |  |

|---------------------------------------------------------------------------------------------------------|--------|-----------|------|----------|-------|-----------------|--|

| Input Voltage Low                                                                                       | VIL    |           |      |          |       |                 |  |

| +5 V tolerant                                                                                           |        | 0         | _    | 0.8      | V     |                 |  |

| +5 V tolerant hysteresis                                                                                |        | 0         | _    | 0.3 *VGG | V     |                 |  |

| Input Voltage High                                                                                      | VIH    |           | _    |          | V     |                 |  |

| +5 V tolerant                                                                                           |        | 2         | _    | 5.25     | V     |                 |  |

| +5 V tolerant hysteresis                                                                                |        | 0.7 * VDD | _    | 5.25     | V     |                 |  |

| Input Hysteresis                                                                                        | VH     |           | _    |          | V     |                 |  |

| +3V hysteresis                                                                                          |        | 0.5       | -    |          | V     |                 |  |

| +5 V tolerant, hysteresis                                                                               |        | 0.3       | _    |          | V     |                 |  |

| Output Voltage Low                                                                                      | VOL    |           |      |          |       |                 |  |